Flip Chip Package Market

Flip Chip Package Market Size, Scope, Growth, Trends and By Segmentation Types, Applications, Regional Analysis and Industry Forecast (2025-2033)

Report ID : RI_705833 | Last Updated : August 17, 2025 |

Format : ![]()

![]()

![]()

![]()

Flip Chip Package Market Size

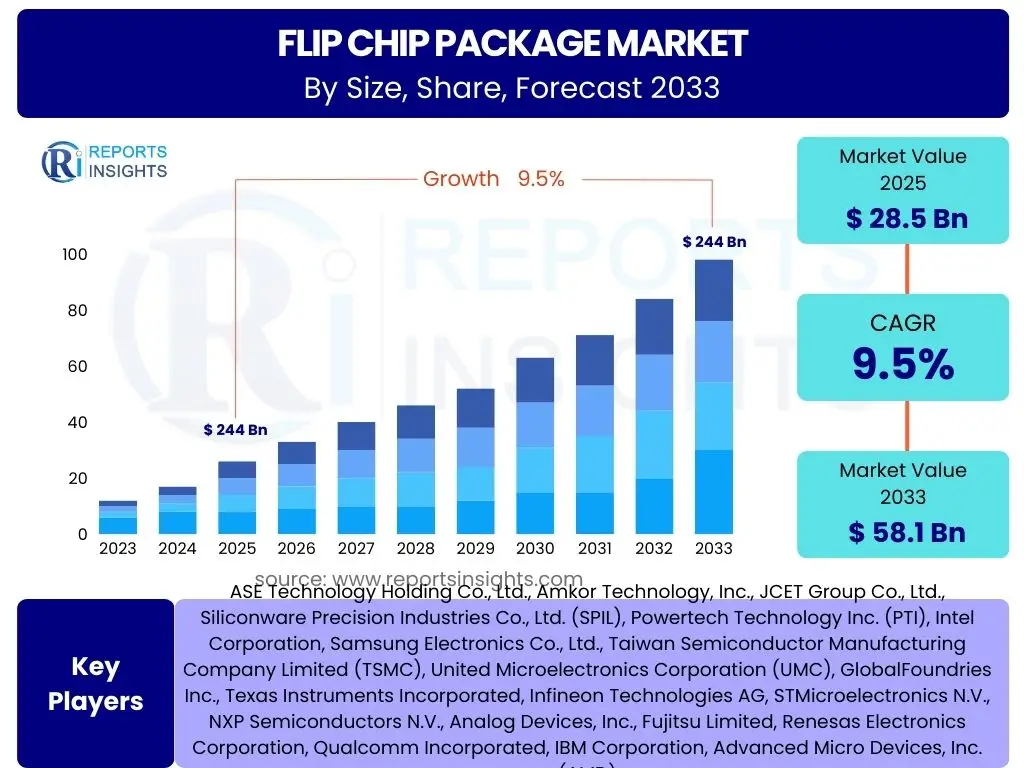

According to Reports Insights Consulting Pvt Ltd, The Flip Chip Package Market is projected to grow at a Compound Annual Growth Rate (CAGR) of 9.5% between 2025 and 2033. The market is estimated at USD 28.5 billion in 2025 and is projected to reach USD 58.1 billion by the end of the forecast period in 2033.

Key Flip Chip Package Market Trends & Insights

User queries frequently center on the evolving technological landscape and adoption patterns within the Flip Chip Package market. Key themes emerging from these inquiries highlight a relentless drive towards miniaturization, higher performance, and enhanced integration capabilities. The market is witnessing a significant shift towards advanced packaging techniques that are critical for enabling next-generation electronic devices, particularly in areas demanding high computational power and bandwidth. This trend is further fueled by the proliferation of sophisticated applications that require compact, efficient, and reliable semiconductor solutions.

Another prominent area of interest pertains to the material science advancements and manufacturing innovations supporting flip chip technology. There is a growing focus on developing new interconnect materials, improving bumping processes, and optimizing thermal management solutions to address the challenges posed by increased power densities and shrinking package sizes. Additionally, the market is observing a strong trend towards heterogeneous integration, where diverse chiplets are combined within a single package, leveraging flip chip as a foundational technology for achieving unprecedented levels of functionality and performance across various end-use sectors.

Furthermore, user insights reveal a keen awareness of the industry's strategic responses to global supply chain dynamics and sustainability imperatives. Companies are increasingly investing in resilient manufacturing capabilities and exploring environmentally conscious production methods, including lead-free solder technologies and energy-efficient processes. The continuous pursuit of cost-effectiveness while maintaining superior performance and reliability remains a core driver, shaping competitive strategies and fostering innovation across the flip chip ecosystem.

- Continued Miniaturization and High-Density Interconnects.

- Proliferated Adoption in High-Performance Computing (HPC) and AI Processors.

- Shift Towards Heterogeneous Integration and Chiplet Architectures.

- Emphasis on Advanced Thermal Management Solutions.

- Development of Lead-Free and Environmentally Compliant Materials.

AI Impact Analysis on Flip Chip Package

User inquiries concerning the impact of Artificial Intelligence (AI) on the Flip Chip Package market reveal a dual perspective: AI as a primary demand driver and AI as an enabler of manufacturing and design efficiencies. The surging demand for AI-specific hardware, including Graphics Processing Units (GPUs), Application-Specific Integrated Circuits (ASICs), and Field-Programmable Gate Arrays (FPGAs) designed for machine learning and deep learning workloads, directly propels the need for advanced packaging solutions like flip chips. These AI accelerators require high-density interconnects, superior electrical performance, and efficient thermal dissipation, attributes that flip chip technology inherently provides. The continuous innovation in AI hardware directly translates into a sustained and growing market for flip chip packages.

Beyond driving demand, AI is increasingly being leveraged within the semiconductor manufacturing process itself, significantly impacting the production and quality of flip chip packages. AI-powered algorithms are deployed for intricate defect detection, yield optimization, and predictive maintenance on manufacturing lines, leading to higher throughput and reduced waste. Furthermore, AI and machine learning techniques are revolutionizing the design and simulation phases of flip chip packages. This includes optimizing interconnect layouts for minimal signal loss, simulating thermal performance under various operating conditions, and predicting package reliability, thereby accelerating the design cycle and improving product quality.

The pervasive integration of AI into various applications, from cloud-based data centers and autonomous vehicles to edge computing and Internet of Things (IoT) devices, ensures a sustained influence on the flip chip market. As AI capabilities expand into more compact and energy-efficient forms, the demand for highly integrated, small-form-factor flip chip packages will only intensify. This symbiotic relationship, where AI drives the need for advanced packaging and simultaneously enhances its development and manufacturing, positions AI as a transformative force within the flip chip industry, fostering continuous innovation and market expansion.

- Increased Demand for High-Performance AI Processors.

- AI-Driven Optimization of Manufacturing Processes and Yield.

- Advancements in AI-Assisted Package Design and Thermal Simulation.

- Growth of Edge AI and IoT Devices Requiring Compact Packaging.

- New Material and Design Innovations Driven by AI Hardware Requirements.

Key Takeaways Flip Chip Package Market Size & Forecast

User inquiries about the essential insights derived from the Flip Chip Package market size and forecast consistently point to the market's robust growth trajectory and its pivotal role in the modern electronics landscape. A primary takeaway is the significant Compound Annual Growth Rate (CAGR) projected through 2033, indicating a healthy and expanding market driven by fundamental technological needs. This sustained growth underscores the increasing reliance on flip chip technology to meet the demands for higher integration density, improved electrical performance, and enhanced thermal management across a broad spectrum of electronic applications. The forecast clearly illustrates that flip chip packaging is not merely a niche technology but a foundational component enabling the evolution of high-performance computing, advanced consumer electronics, and emerging industrial applications.

A crucial insight gleaned from the market forecast is the strong correlation between the adoption of next-generation technologies and the demand for flip chip packages. Sectors such as artificial intelligence, 5G communication, automotive electronics, and the Internet of Things (IoT) are identified as primary accelerators of market expansion. The inherent advantages of flip chip—including its ability to support higher I/O counts, reduce package size, and offer superior electrical characteristics compared to traditional wire bonding—make it indispensable for these technologically advanced and computationally intensive applications. The forecast therefore reflects a market poised for continued innovation and integration into new and expanding segments of the electronics industry.

Furthermore, the market's growth trajectory signals ongoing investment in research and development, particularly in areas like advanced bumping technologies, substrate materials, and assembly processes. This continuous innovation is vital for addressing current challenges and unlocking new opportunities, ensuring the flip chip package market remains competitive and adaptable to future technological shifts. The sustained financial growth projected within the forecast period reinforces the strategic importance of flip chip packaging as a critical enabler for the miniaturization and performance enhancement required by the increasingly complex and powerful electronic devices of tomorrow, affirming its status as a cornerstone of semiconductor advancement.

- Substantial Market Expansion Driven by Technology Advancements.

- Critical Role in Enabling High-Performance Computing and AI.

- Growing Adoption Across Diverse End-Use Industries.

- Continuous Innovation in Bumping and Interconnect Technologies.

- Strategic Importance for Miniaturization and Efficiency in Electronics.

Flip Chip Package Market Drivers Analysis

The Flip Chip Package market is propelled by several potent drivers stemming from the evolving demands of the global electronics industry. The relentless pursuit of device miniaturization and the need for higher integration density in electronic components are paramount, as flip chip technology enables more input/output (I/O) connections in a smaller footprint than traditional wire bonding. This capability is critical for compact and sophisticated devices such as smartphones, wearables, and high-performance computing units. Concurrently, the escalating demand for high-performance computing (HPC) and artificial intelligence (AI) processors necessitates packaging solutions that can handle increased power, dissipate heat efficiently, and support high-speed data transfer, all of which are core strengths of flip chip technology. The proliferation of 5G infrastructure and advanced automotive electronics, including ADAS and infotainment systems, further amplifies this demand, making flip chip an indispensable technology for these rapidly expanding sectors.

| Drivers | (~) Impact on CAGR % Forecast | Regional/Country Relevance | Impact Time Period |

|---|---|---|---|

| Increased demand for miniaturization and higher integration in electronic devices. | +2.1% | Global, particularly Asia Pacific (APAC) consumer electronics hubs | 2025-2033 |

| Rising adoption of high-performance computing (HPC) and AI processors. | +1.8% | North America, Europe, Asia Pacific (China, Taiwan, South Korea) | 2025-2033 |

| Growth of the automotive electronics sector (ADAS, infotainment, EVs). | +1.5% | Europe, North America, Asia Pacific (Japan, China, South Korea) | 2026-2033 |

| Expansion of 5G infrastructure and Internet of Things (IoT) devices. | +1.3% | Global, with strong impetus in Asia Pacific and North America | 2025-2030 |

| Cost-effectiveness and performance benefits over traditional packaging. | +0.8% | Global, especially emerging markets seeking efficiency | 2025-2033 |

Flip Chip Package Market Restraints Analysis

Despite its significant advantages, the Flip Chip Package market faces several notable restraints that could temper its growth trajectory. The primary challenge is the high initial investment required for sophisticated manufacturing equipment and specialized facilities. The complexity of the flip chip assembly process, involving precise bumping, alignment, and bonding, necessitates advanced cleanroom environments and skilled labor, leading to higher upfront capital expenditures compared to traditional packaging methods. This can be a barrier to entry for new players and limit expansion for smaller enterprises. Additionally, managing the thermal output of high-power flip chip components remains a critical concern. As devices become more integrated and powerful, dissipating the generated heat efficiently becomes increasingly difficult, potentially leading to reliability issues or requiring expensive, complex thermal management solutions that add to the overall cost and design complexity.

| Restraints | (~) Impact on CAGR % Forecast | Regional/Country Relevance | Impact Time Period |

|---|---|---|---|

| High initial investment and manufacturing complexity. | -1.2% | Global, particularly smaller manufacturers | 2025-2030 |

| Challenges in thermal management for high-power applications. | -0.9% | Global, especially for HPC and AI applications | 2025-2033 |

| Competition from alternative advanced packaging technologies (e.g., Fan-Out Wafer Level Packaging). | -0.7% | Asia Pacific (Taiwan, South Korea), North America | 2025-2033 |

| Potential for warpage and reliability issues in large, complex packages. | -0.5% | Global, particularly for high-end chip designs | 2027-2033 |

| Dependence on a highly specialized and skilled workforce. | -0.4% | North America, Europe, parts of Asia requiring specific expertise | 2025-2033 |

Flip Chip Package Market Opportunities Analysis

Significant opportunities are emerging within the Flip Chip Package market, driven by the continuous evolution of electronics and the strategic global focus on semiconductor independence. The proliferation of new and niche applications presents a substantial growth avenue; sectors such as augmented reality (AR), virtual reality (VR), quantum computing, and advanced medical devices are increasingly demanding compact, high-performance, and low-latency integrated circuits, for which flip chip technology is ideally suited. These emerging areas represent untapped markets where flip chip can offer distinct advantages over traditional packaging methods, fostering innovation and specialized product development. Furthermore, ongoing advancements in materials science and interconnect technologies, including novel solder alloys, bonding techniques, and substrate materials, continue to expand the performance boundaries and applicability of flip chip packages, opening doors to more efficient and reliable designs.

| Opportunities | (~) Impact on CAGR % Forecast | Regional/Country Relevance | Impact Time Period |

|---|---|---|---|

| Emergence of new applications in AR/VR, quantum computing, and advanced medical devices. | +1.9% | North America, Europe, Asia Pacific (Japan, South Korea) | 2026-2033 |

| Development of advanced materials and interconnect technologies. | +1.6% | Global, particularly R&D hubs | 2025-2033 |

| Strategic partnerships and collaborations for R&D and manufacturing. | +1.2% | Global, especially cross-regional collaborations | 2025-2033 |

| Government incentives and investments in domestic semiconductor manufacturing. | +1.0% | North America, Europe, Asia Pacific (e.g., CHIPS Acts) | 2025-2030 |

| Integration into System-in-Package (SiP) and heterogeneous integration solutions. | +0.8% | Global, driven by miniaturization trends | 2025-2033 |

Flip Chip Package Market Challenges Impact Analysis

The Flip Chip Package market faces several significant challenges that necessitate strategic responses from industry players. A primary concern is maintaining consistently high yield and reliability for increasingly complex designs, especially as die sizes grow and interconnect densities escalate. The intricate nature of flip chip assembly means that even minor process variations can lead to defects, impacting overall product quality and increasing manufacturing costs. This demands continuous innovation in process control, quality assurance, and inspection technologies. Furthermore, the market is highly susceptible to global supply chain disruptions and geopolitical tensions. Dependencies on specific regions for raw materials, specialized equipment, or manufacturing capacities can create vulnerabilities, leading to delays, increased costs, and potential production bottlenecks, which were acutely observed during recent global events. Navigating these external pressures requires robust supply chain management and diversification strategies.

| Challenges | (~) Impact on CAGR % Forecast | Regional/Country Relevance | Impact Time Period |

|---|---|---|---|

| Maintaining yield and reliability for increasingly complex designs. | -1.1% | Global, especially for leading-edge technologies | 2025-2033 |

| Managing supply chain disruptions and geopolitical tensions. | -1.0% | Global, with specific impact on regions heavily reliant on imports/exports | 2025-2028 |

| Skilled labor shortages in advanced packaging technologies. | -0.8% | North America, Europe, parts of Asia | 2025-2033 |

| Evolving environmental regulations and material restrictions. | -0.6% | Europe, North America, parts of Asia enforcing stricter rules | 2027-2033 |

| High research and development costs for next-generation solutions. | -0.5% | Global, impacting smaller players disproportionately | 2025-2033 |

Flip Chip Package Market - Updated Report Scope

This comprehensive report delves into the intricate dynamics of the Flip Chip Package market, providing an exhaustive analysis of its current landscape, historical performance, and future projections. The scope encompasses detailed market sizing, trend analysis, and an in-depth examination of the key drivers, restraints, opportunities, and challenges shaping the industry. It offers a granular segmentation across various technological aspects, packaging types, applications, and end-use industries, providing stakeholders with a clear understanding of market opportunities. The report also highlights regional market insights and profiles the leading companies driving innovation and competition within the global flip chip ecosystem.

| Report Attributes | Report Details |

|---|---|

| Base Year | 2024 |

| Historical Year | 2019 to 2023 |

| Forecast Year | 2025 - 2033 |

| Market Size in 2025 | USD 28.5 billion |

| Market Forecast in 2033 | USD 58.1 billion |

| Growth Rate | 9.5% |

| Number of Pages | 247 |

| Key Trends |

|

| Segments Covered |

|

| Key Companies Covered | ASE Technology Holding Co., Ltd., Amkor Technology, Inc., JCET Group Co., Ltd., Siliconware Precision Industries Co., Ltd. (SPIL), Powertech Technology Inc. (PTI), Intel Corporation, Samsung Electronics Co., Ltd., Taiwan Semiconductor Manufacturing Company Limited (TSMC), United Microelectronics Corporation (UMC), GlobalFoundries Inc., Texas Instruments Incorporated, Infineon Technologies AG, STMicroelectronics N.V., NXP Semiconductors N.V., Analog Devices, Inc., Fujitsu Limited, Renesas Electronics Corporation, Qualcomm Incorporated, IBM Corporation, Advanced Micro Devices, Inc. (AMD) |

| Regions Covered | North America, Europe, Asia Pacific (APAC), Latin America, Middle East, and Africa (MEA) |

| Speak to Analyst | Avail customised purchase options to meet your exact research needs. Request For Analyst Or Customization |

Segmentation Analysis

The Flip Chip Package market is comprehensively segmented to provide granular insights into its diverse components and applications. This segmentation highlights the various technological approaches, packaging formats, and end-use sectors that collectively define the market landscape. Understanding these segments is crucial for identifying specific growth drivers, assessing competitive dynamics, and pinpointing emerging opportunities across the value chain. The market's complexity is reflected in its multiple dimensions, ranging from the fundamental bumping technologies used to the broad array of applications that leverage flip chip advantages.

- By Bumping Technology: Solder Bumping, Gold Bumping, Copper Pillar Bumping

- By Packaging Type: Flip Chip Ball Grid Array (FC-BGA), Flip Chip Chip Scale Package (FC-CSP), Flip Chip Pin Grid Array (FC-PGA), Others

- By Application: Smartphones, Tablets, Laptops, Automotive, Industrial, Data Centers, AI/High Performance Computing (HPC), Consumer Electronics, Internet of Things (IoT), Medical Devices

- By End-Use Industry: Electronics, Automotive, Industrial, Healthcare, Telecommunications, Others

Regional Highlights

- North America: This region is a significant hub for research and development in advanced semiconductors and high-performance computing. It is characterized by the presence of major fabless companies and technology innovators, driving demand for cutting-edge flip chip solutions, particularly in data centers, AI, and defense applications.

- Europe: Europe exhibits strong growth in automotive electronics, industrial automation, and specialized high-reliability applications. The region's emphasis on stringent quality standards and robust semiconductor manufacturing initiatives contributes to the steady adoption of flip chip technology.

- Asia Pacific (APAC): APAC dominates the global semiconductor manufacturing and consumer electronics market, making it the largest and fastest-growing region for flip chip packages. Countries like Taiwan, South Korea, China, and Japan are at the forefront of semiconductor production, assembly, and packaging, fueled by high volume manufacturing for smartphones, tablets, and a burgeoning automotive sector. The region's extensive infrastructure and investment in advanced packaging technologies are pivotal to market expansion.

- Latin America: While a smaller market, Latin America is experiencing gradual growth, primarily driven by increasing penetration of consumer electronics and expanding automotive manufacturing capabilities in some countries. The focus is on localized assembly and growing demand for integrated devices.

- Middle East and Africa (MEA): The MEA region is in nascent stages of flip chip adoption, with growth propelled by increasing digital transformation initiatives, investments in telecommunications infrastructure (e.g., 5G rollout), and a rising demand for consumer electronics. Future growth is anticipated as regional economies diversify and industrialization progresses.

Top Key Players

The market research report includes a detailed profile of leading stakeholders in the Flip Chip Package Market.- ASE Technology Holding Co., Ltd.

- Amkor Technology, Inc.

- JCET Group Co., Ltd.

- Siliconware Precision Industries Co., Ltd. (SPIL)

- Powertech Technology Inc. (PTI)

- Intel Corporation

- Samsung Electronics Co., Ltd.

- Taiwan Semiconductor Manufacturing Company Limited (TSMC)

- United Microelectronics Corporation (UMC)

- GlobalFoundries Inc.

- Texas Instruments Incorporated

- Infineon Technologies AG

- STMicroelectronics N.V.

- NXP Semiconductors N.V.

- Analog Devices, Inc.

- Fujitsu Limited

- Renesas Electronics Corporation

- Qualcomm Incorporated

- IBM Corporation

- Advanced Micro Devices, Inc. (AMD)

Frequently Asked Questions

Analyze common user questions about the Flip Chip Package market and generate a concise list of summarized FAQs reflecting key topics and concerns.What is a flip chip package?

A flip chip package is an advanced semiconductor packaging technology where the semiconductor die is inverted (flipped over) and connected directly to a substrate or circuit board using tiny conductive bumps (typically solder or copper) instead of traditional wire bonds. This direct electrical connection minimizes signal path length, reduces package size, and allows for a higher density of interconnections, enabling superior electrical performance, enhanced thermal dissipation, and overall smaller form factors for integrated circuits. It is widely used for high-performance processors and memory chips.

What are the primary advantages of flip chip technology over traditional wire bonding?

Flip chip technology offers several significant advantages over traditional wire bonding. Key benefits include greatly reduced package size and weight due to the absence of bonding wires and the ability to connect the entire surface of the die. It enables higher input/output (I/O) counts, crucial for complex, high-performance integrated circuits. Electrical performance is enhanced through shorter signal paths and lower inductance, leading to faster operating speeds. Additionally, flip chip designs often provide better thermal dissipation due to the direct metal-to-metal contact with the substrate, contributing to improved reliability and longevity of the packaged device.

What are the key applications for flip chip packages?

Flip chip packages are extensively used across a broad range of high-performance and miniaturized electronic applications. Major applications include smartphones, tablets, and laptops, where compact size and high functionality are critical. They are indispensable in high-performance computing (HPC) for central processing units (CPUs), graphics processing units (GPUs), and specialized AI accelerators, due to their superior electrical and thermal characteristics. Other significant applications include advanced automotive electronics (e.g., ADAS, infotainment systems), industrial equipment, data centers, and various Internet of Things (IoT) devices that demand efficient and reliable semiconductor integration.

What challenges are associated with flip chip manufacturing and adoption?

Despite its benefits, flip chip manufacturing and adoption present several challenges. These include high initial capital investment for specialized equipment and facilities, particularly for precision bumping and assembly processes. The technology demands extremely tight process control and high precision to maintain yield and reliability, especially with increasing interconnect density. Thermal management is also a significant challenge for high-power flip chip devices, requiring sophisticated cooling solutions. Furthermore, potential issues like warpage of large packages and the need for a highly skilled workforce add to the complexity and cost of implementation.

What are the future trends expected to impact the flip chip package market?

Future trends in the flip chip package market are driven by continuous advancements in semiconductor technology and evolving application demands. Key trends include the widespread adoption of heterogeneous integration and chiplet architectures, where multiple different dies are interconnected within a single package using flip chip. There will be increased focus on advanced thermal management solutions to handle higher power densities. Innovations in bumping technologies, such as micro-bumps and hybrid bonding, will enable even higher interconnect densities. Additionally, the market will see continued growth in demand from AI, 5G, and automotive sectors, alongside a push for more sustainable and environmentally friendly manufacturing processes.